| 简单记录UART/I2C/SPI/DDR/AXI/PCIE通信协议 | 您所在的位置:网站首页 › pci 与pcie › 简单记录UART/I2C/SPI/DDR/AXI/PCIE通信协议 |

简单记录UART/I2C/SPI/DDR/AXI/PCIE通信协议

|

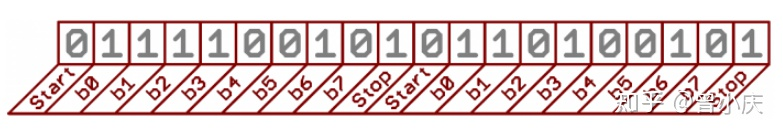

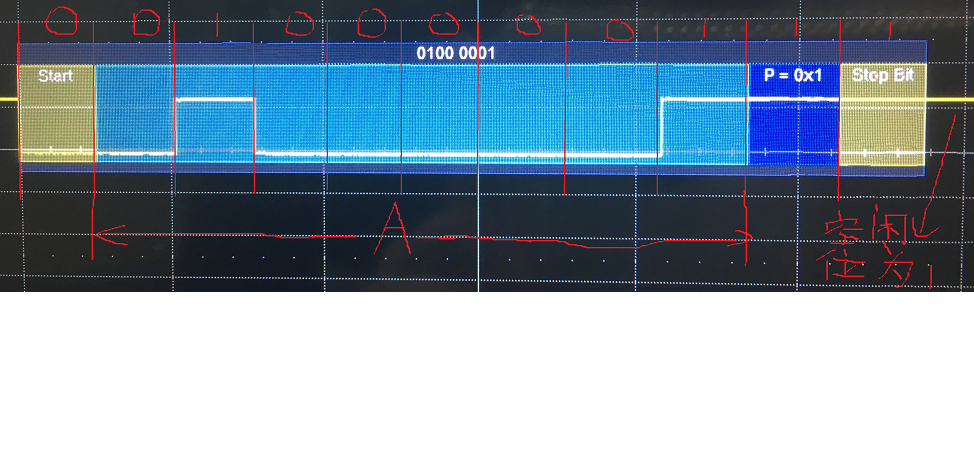

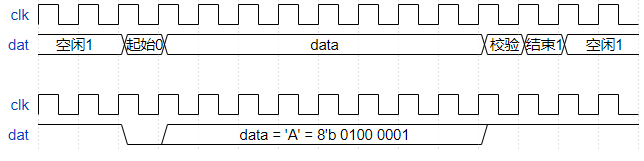

单工:简单的说就是一方只能发信息,另一方则只能收信息,通信是单向的。 半双工:比单工先进一点,就是双方都能发信息,但同一时间则只能一方发信息。 全双工:比半双工再先进一点,就是双方不仅都能发信息,而且能够同时发送。 UART通用异步收发器(Universal Asynchronous Receiver/Transmitter) 串行、异步、全双工的通信协议 只需要一条线即可完成通信。两条线可以实现全双工通信。 空闲位1 + 起始位0 + 数据位 + 奇偶校验位(可选) + 停止位1 + 空闲位1 串口发送数据很像田径比赛,发令员手举旗子拿着哨子,然后吹哨+放下旗子(拉低电平),信号开始往前冲,然后终点线是一个高高的线(高电平),冲线,胜利^o^y 数据传输速率使用波特率来表示。单位bps(bits per second) 异步:通俗说是两个uart设备之间通信的时候不需要时钟线,这时候就需要在两个uart设备上指定相同的传输速率,以及空闲位、起始位、校验位、结束位,也就是遵循相同的协议。 –> USART:名字里多了个同步。 使用USART在异步通信的时候,它与UART没有什么区别,但是用在同步通信的时候,区别就很明显了:大家都知道同步通信需要时钟来触发数据传输,也就是说USART相对UART的区别之一就是能提供主动时钟。来自:uart与usart区别 - coolyouguo - 博客园 这个文章写的很好: UART串口协议详解 - 知乎

UART协议详解 - 者旨於陽 - 博客园 UART协议详解_GQ1900的博客-CSDN博客_uart协议 自己画了个波形图:

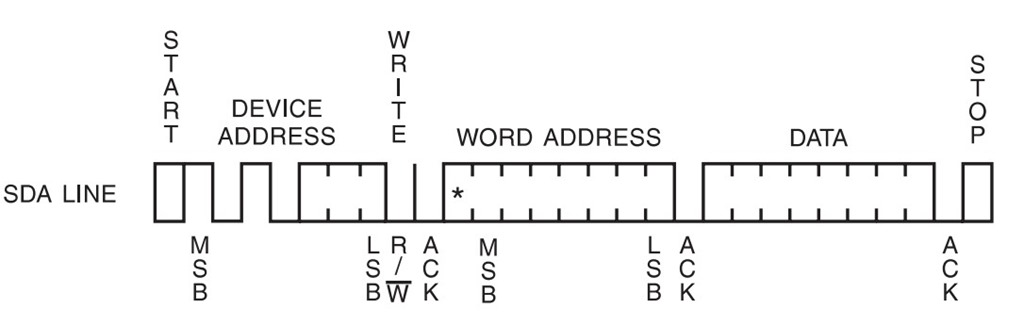

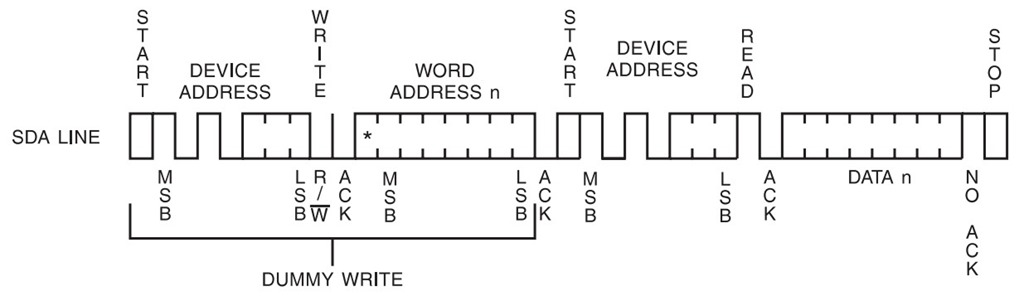

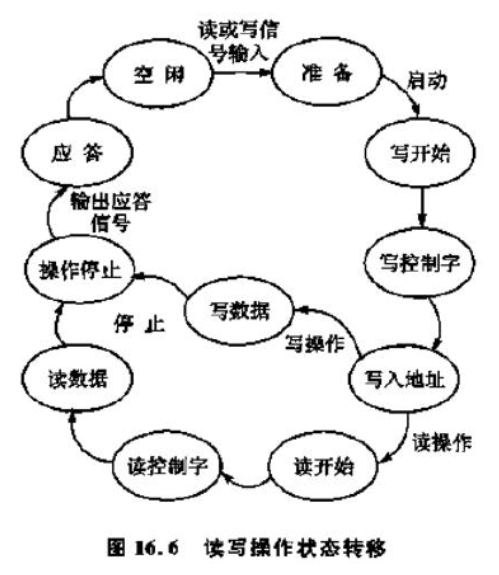

波形代码: {signal: [ {name: 'clk', wave: 'p..............'}, {name: 'dat', wave: '=.==.......===.', data: ['空闲1','起始0','data','校验','结束1','空闲1']}, {}, {name: 'clk', wave: 'p..............'}, {name: 'dat', wave: '1.0=.......1...', data: ['data = \'A\' = 8\'b 0100 0001']}, ]}波形图生成自:WaveDrom Editor I2CI2C(Inter-Integrated Circuit BUS) 集成电路总线 串行,同步,双线,半双工。 SCL串行时钟信号,SDA串行数据(/地址)信号 启动:SCL为高时,SDA下拉 停止:SCL为高时,SDA上拉 传输数据:SCL为高时,SDA不能动(保持稳定) 准备数据:SCL为低时,SDA可以准备数据 应答(ACK,Acknowledgement) 写时序: 读时序: I2C是物理层+协议层。 下面参考博文介绍了物理层。 参考:IIC通信协议总结_zhc的博客-CSDN博客_iic协议

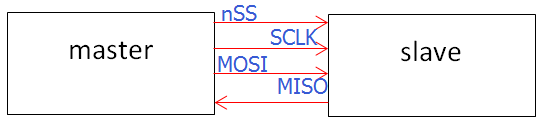

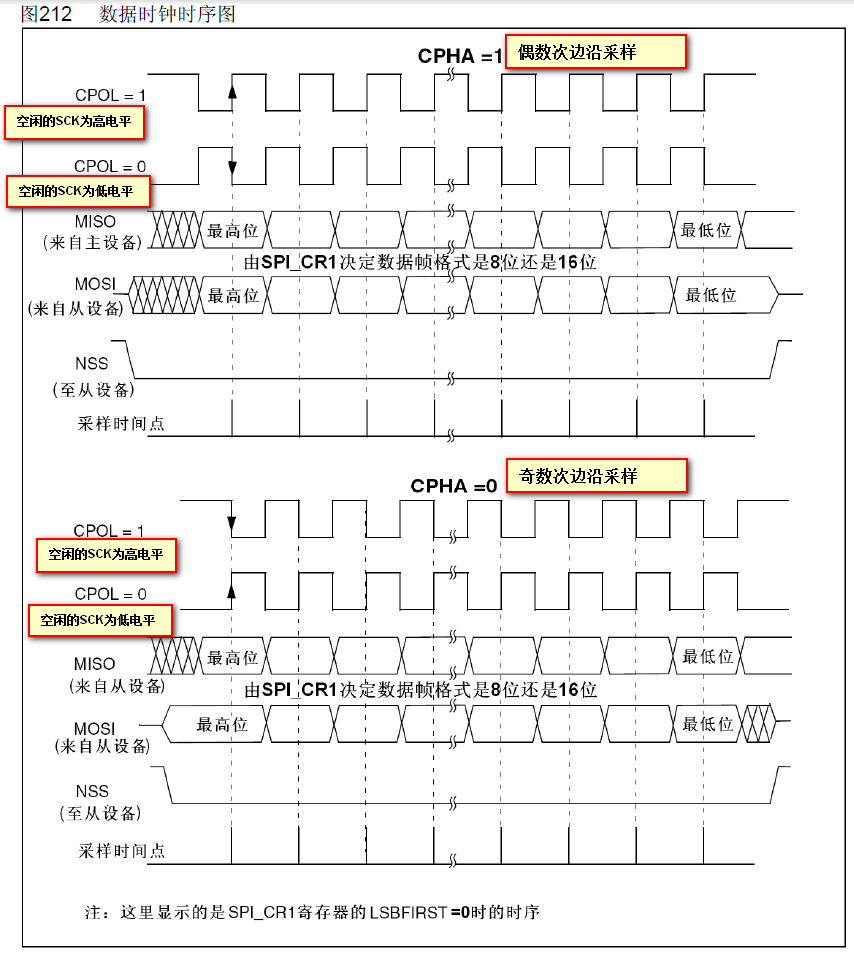

SPI(Serial peripheral interface)即串行外围设备接口。 串行,同步,高速,全双工。四线。

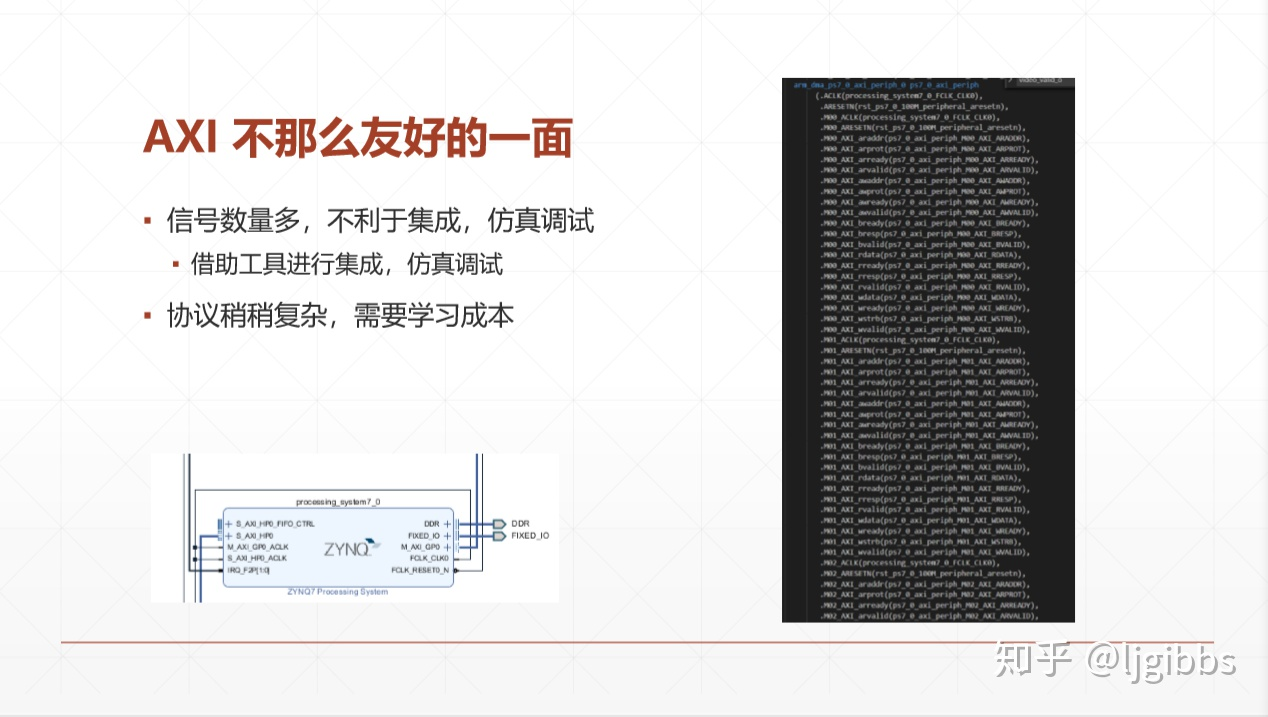

通讯的起始/结束信号 nSS信号由高电平变为低电平即为SPI通讯的起始信号,反过来,nSS信号由低电平变为高电平即为SPI通讯的结束信号。比I2C简单。当从机检测到自身的nSS引脚被拉低时就知道自己被主机选中,准备和主机进行通讯。 有效数据的采集 参考:SPI通讯协议介绍_echo_bright_的博客-CSDN博客_spi协议 SPI协议的优缺点: 优点 协议简单利于硬件设计与实现,比如不需要像I2C协议中每个从器件都需要一个地址;只用到4根线,封装也很容易做 全双工的协议,既能发送数据也能接受数据 三态输出的驱动能力强,相对I2C的开漏输出,抗干扰能力强,传输稳定; 相对于I2C协议,时钟速度快,没有最大限制 输入输出的bit数也没什么限制,不局限于一个byte 缺点 信号线4根,比I2C多,芯片选择线会随着从器件的个数的增加而增加 传输的过程没有确认信号,撸起柚子加油传,不管从器件收不收到;在SPI Flash中会有read status 这个命令确认从器件的状态,是否处于busy状态 没有校验机制,I2C也没有,难兄难弟啊 参考:简单快速的总线协议——SPI - 知乎 DDR不是协议。 DDR, Double Data Rate, 在时钟脉冲的上升沿和下降沿传输数据。 用在内存DRAM(SDRAM)上。 Refer: 深入浅出DDR系列(一)–DDR原理篇_奇小葩-CSDN博客 深入浅出DDR系列(二)–DDR工作原理_奇小葩-CSDN博客 AXI总线一般指信号的集合,协议指的是在总线上的编解码方式 AXI是芯片内部的同步串行总线 外部总线,最常见的操作就是连接两个实体。内部总线连接的是芯片内部的模块。System on Chip 片上系统,在手机的芯片里有我们的处理器核,还有用于渲染画面的 GPU、处理照片的 ISP 、用于调制解调的 DSP 等等,那么这些模块之间都需要总线互联。

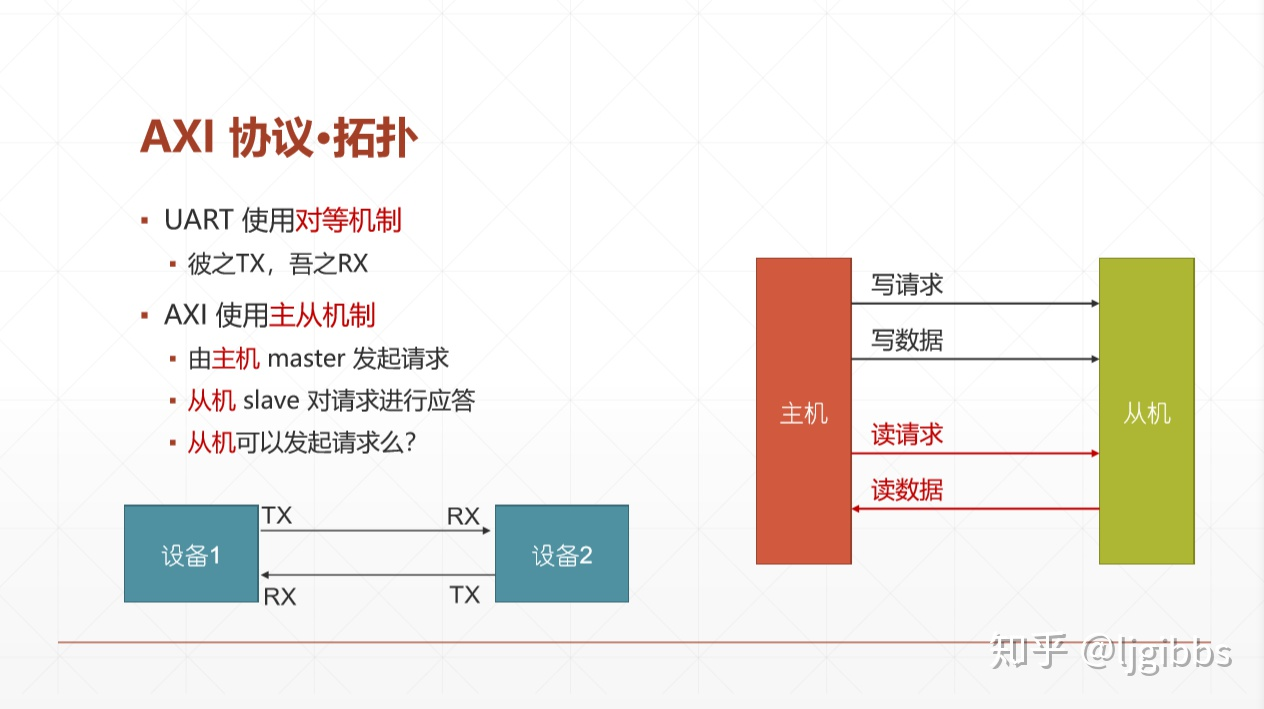

Uart 在两个设备之间是对等的,可以全双工工作。而AXI 相当于一个单工工作模式,信号需要有一个发起方,另一方作为响应方。请求和应答的两方地位实际上是不对等的,分别称为主机与从机。由主机发起请求,从机对请求进行回复。这里提了一个问题:从机是否可以发起读写请求。那么答案是显然不行,从机压根无法驱动发起请求的信号。

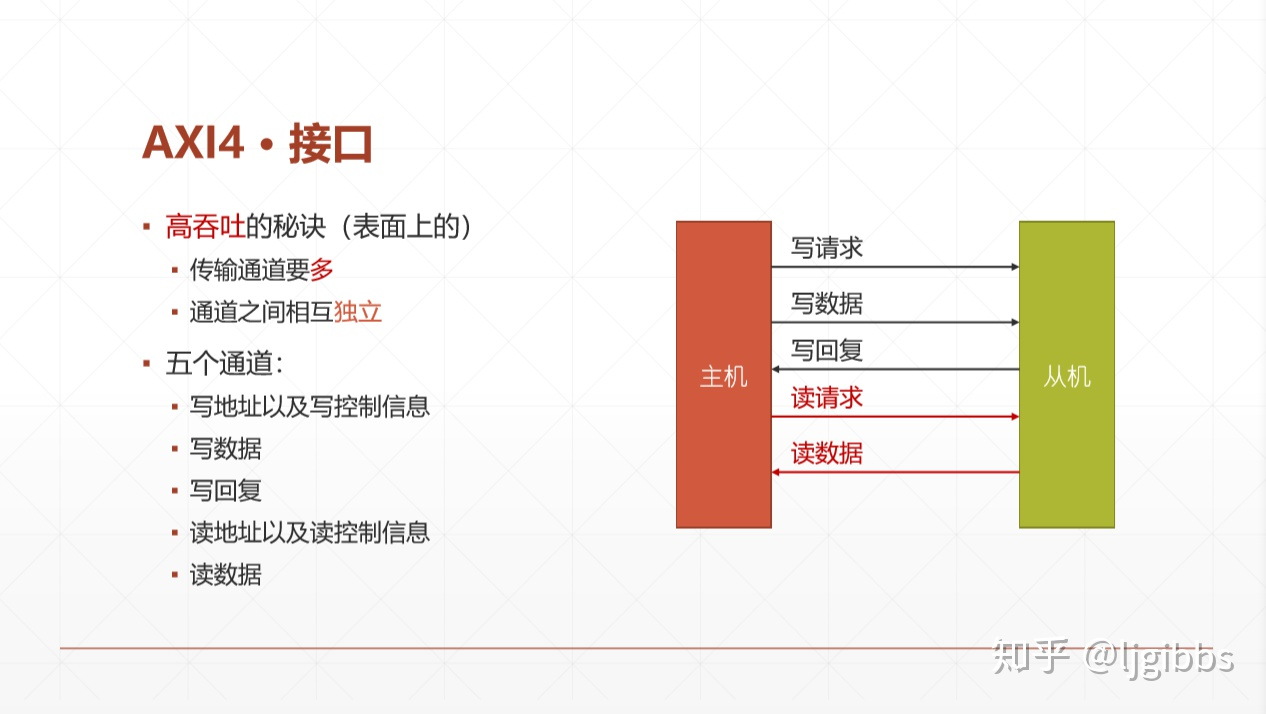

The AXI protocol is burst-based and defines the following independent transaction channels: • read address 读地址 • read data 读数据 • write address 写地址 • write data 写数据 • write response 写回复

深入 AXI4 总线(B)附录·一次从〇开始的 AXI 总线入门研讨 - ljgibbs的文章 - 知乎 深入 AXI4 总线(O)专栏目录与资料集合 - 知乎 深入 AXI4 总线(一)握手机制 - 知乎 深入 AXI4 总线(二)架构 - 知乎

AMBA协议家族中有 AHB APB 这些用于 processor 的总线,他们一般很高冷,和我们 FPGA 的 ip 核们很少打交道。 AXI4-Lite和AXI4-Stream协议 用通俗的说法,Lite 是标准 AXI4 协议被砍了几刀的结果。AXI4-Lite 的使用场景主要用于寄存器的配置,这也就是为什么数据通道的宽度被设置为 32 位或者 64 位了。 首先 AXI4-Stream 砍去了地址概念,Stream 将不再是一种 address mapped 的协议,而是一种点对点(或者一点对多点)数据流通信的协议。打个比方, AXI4 适合访问诸如 RAM 等有地址概念的存储介质,而 Stream 协议则适合访问诸如 FIFO 这样没有地址概念的存储介质。 Stream 协议的读写通道也是单向的,但信号是完全一致的,Stream 协议中不再存在读写通道的区别,也不再有独立的写回复通道。 深入 AXI4总线(C1)旧版存档:AXI4 的兄弟协议 - 知乎

印象中用于显卡。 |

【本文地址】

参考:IIC协议学习笔记 - 知乎

参考:IIC协议学习笔记 - 知乎

适用于一主机多从机场景。四条线:nSS(片选),SCLK时钟,MOSI(主机到从机的数据),MISO(从机到主机的数据)

适用于一主机多从机场景。四条线:nSS(片选),SCLK时钟,MOSI(主机到从机的数据),MISO(从机到主机的数据)

AXI 总线实现的面积比较大。

AXI 总线实现的面积比较大。